# FACULTY OF PHYSICS AND ASTRONOMY RUPERTUS CAROLA UNIVERSITY OF HEIDELBERG

Diploma Thesis

in Physics

submitted by

Jan Becker

born in Hamburg (Germany)

2000

# The Data Aquisition and Control System for a Fast Trigger at H1

This diploma thesis has been carried out by Jan Becker at the

Institute of Physics

under the supervision of

Prof. Dr. Franz Eisele

#### The Data Aquisition and Control System for a Fast Trigger at H1

The HERA (Hadron-Elektron-Ring-Anlage) particle collider at DESY in Hamburg (Germany) is operating since May 1992. An upgrade for HERA is planned for 2000/2001 to gain higher luminosity. A bigger number of background events is therefore also expected. A new fast trigger called CIP2000 trigger is developed to examine and suppress the background events. The trigger system uses the pad information of five cylindrical multiwire chambers to calculate a histogramm of track origins along the beam axis. From the structure of this histogram background events can be identified. The aim of this diploma thesis is to develop and test the control system and the readout system for the new trigger. The communication between the different CPUs (pVIC) and the communication between the CPUs and the newly designed trigger cards (VME) are tested in a test system. Different data reduction algorithms to reduce the size of the read out events are simulated. The connection and communication of the STC (Subsystem Trigger Control) system and the CIP2000 trigger system is defined and some parts of the communication are tested. The control system for the whole CIP2000 trigger system is specified.

#### Das Datennahme- und Kontrollsystem für einen schnellen Trigger bei H1

Der HERA (Hadron-Elektron-Ring-Anlage) Elektron-Proton-Speicherring am DESY in Hamburg (Deutschland) ist seit Mai 1992 in Betrieb. Eine Erhöhung der Luminosität von HERA ist für die Jahre 2000/2001 geplant. Deshalb wird auch eine größere Anzahl von Untergrundereignissen erwartet. Ein neuer schneller Trigger (CIP2000 Trigger) wurde entwickelt, um die Untergrundereignisse zu untersuchen und zu unterdrücken. Das Triggersystem benutzt die Kammerinformationen von fünf zylindrischen Kammern, um ein Histogramm der rekonstruierten Spurursprünge entlang der Strahlachse zu berechnen. An der Struktur dieses Histogramms können Untergrundereignisse erkannt werden. Das Ziel dieser Diplomarbeit ist die Entwicklung und der Test eines Kontroll- und Datennahmesystems für den neuen Trigger. Die Kommunikation der verschiedenen CPUs (pVIC) und die Kommunikation zwischen den CPUs und den neu entwickelten Triggerkarten (VME) wurde an Hand eines Testsystems untersucht. Verschiedene Datenreduktionsalgorithmen wurden simuliert, um die ausgelesene Datenmenge zu verkleinern. Die Verbindung des STC-Systems (Subsystem Trigger Control) mit dem CIP2000 Triggersystem wurde definiert und Teile dieser Verbindung getestet. Ein Kontrollsystem für das gesamte CIP2000 Triggersystem wurde entwickelt.

# Contents

| 1 | Intr | oducti | on                                        | 1  |

|---|------|--------|-------------------------------------------|----|

| 2 | HEI  | RA an  | d the H1 detector                         | 3  |

|   | 2.1  | The H  | ERA machine                               | 3  |

|   | 2.2  | The H  | 1 detector                                | 4  |

|   |      | 2.2.1  | H1 trigger system                         | 5  |

|   |      | 2.2.2  | H1 readout system                         | 7  |

|   | 2.3  | The H  | 1 upgrade for HERA 2000                   | 8  |

| 3 | The  | CIP2   | 000 trigger system                        | 10 |

|   | 3.1  | Motiva | ation                                     | 10 |

|   | 3.2  | Trigge | er algorithm                              | 11 |

|   | 3.3  | Projec | etive geometry                            | 13 |

|   | 3.4  | Trigge | er system implementation                  | 14 |

|   |      | 3.4.1  | Chamber geometry                          | 15 |

|   |      | 3.4.2  | Chamber readout                           | 17 |

|   |      | 3.4.3  | Trigger system hardware                   | 18 |

|   |      | 3.4.4  | Timing                                    | 24 |

| 4 | The  | CIP2   | 000 trigger control system                | 25 |

|   | 4.1  | CIP20  | 00 trigger system control structure       | 25 |

|   | 4.2  | STC s  | ystem                                     | 25 |

|   |      | 4.2.1  | Trigger signals                           | 28 |

|   |      | 4.2.2  | Trigger signal timing                     | 30 |

|   |      | 4.2.3  | STC cards                                 | 33 |

|   | 4 3  | CIP20  | 00 trigger STC and readout control system | 36 |

| 5            | The                              | CIP2    | 000 trigger readout system                        | 38 |

|--------------|----------------------------------|---------|---------------------------------------------------|----|

|              | 5.1                              | Reado   | out system structure                              | 38 |

|              | 5.2                              | Reado   | out system timing                                 | 40 |

|              | 5.3                              | Reado   | out system hardware                               | 42 |

|              |                                  | 5.3.1   | Connection of CPU and trigger card: VME           | 42 |

|              |                                  | 5.3.2   | Trigger card                                      | 44 |

|              |                                  | 5.3.3   | CPU board                                         | 45 |

|              |                                  | 5.3.4   | Connection of CPUs: pVIC                          | 47 |

|              |                                  | 5.3.5   | Connection of main CPU and STC system: VIC        | 48 |

|              |                                  | 5.3.6   | Connection of main CPU and VMEtaxi card: VSB, VIC | 50 |

|              | 5.4                              | Reado   | out system software                               | 50 |

| 6            | Test                             | ts with | the CIP2000 trigger readout test system           | 52 |

|              | 6.1                              | Test o  | f the VME bus                                     | 52 |

|              | 6.2                              | Test o  | f the pVIC bus                                    | 55 |

| 7            | Dat                              | a redu  | ction for the CIP2000 trigger readout             | 58 |

|              | 7.1                              | Raw d   | ata of the CIP2000 trigger                        | 58 |

|              | 7.2                              | Data 1  | reduction algorithms                              | 60 |

|              |                                  | 7.2.1   | Zero supression                                   | 60 |

|              |                                  | 7.2.2   | Run length encoding (RLE)                         | 60 |

|              | 7.3                              | Simula  | ation of data reduction algorithms                | 61 |

|              |                                  | 7.3.1   | Activated pads                                    | 61 |

|              |                                  | 7.3.2   | Data reduction algorithms                         | 63 |

|              |                                  | 7.3.3   | Conclusion                                        | 67 |

| $\mathbf{A}$ | Dict                             | tionary | y of abbreviations                                | 70 |

|              | Bibl                             | liograp | ohy                                               | 72 |

|              | $\mathbf{A}\mathbf{c}\mathbf{k}$ | nowle   | dgements                                          | 74 |

# List of Figures

| 2.1  | The HERA storage ring                                           | 3  |

|------|-----------------------------------------------------------------|----|

| 2.2  | Overview of the H1 detector                                     | 4  |

| 2.3  | H1 trigger levels                                               | 5  |

| 2.4  | Principle of pipelining in H1 subsystems                        | 6  |

| 2.5  | Principle of the H1 detector readout                            | 7  |

| 3.1  | Definition of a local environment                               | 12 |

| 3.2  | Overview of the CIP2000 trigger algorithm                       | 12 |

| 3.3  | Projective geometry                                             | 13 |

| 3.4  | Overview of the CIP2000 trigger system                          | 14 |

| 3.5  | Side view of the CIP2000 chamber                                | 15 |

| 3.6  | Front view of the CIP2000 chamber                               | 16 |

| 3.7  | Signal path of the CIP2000 chamber readout                      | 17 |

| 3.8  | Overview of the CIP2000 chamber readout for 4 sectors in $\phi$ | 18 |

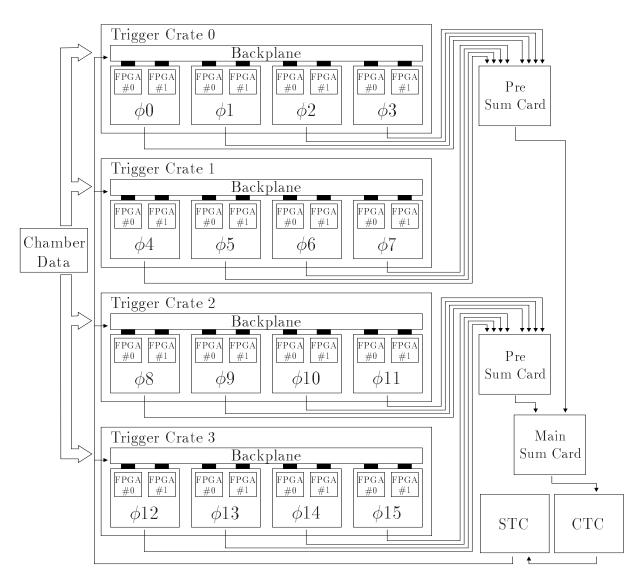

| 3.9  | CIP2000 trigger system structure                                | 19 |

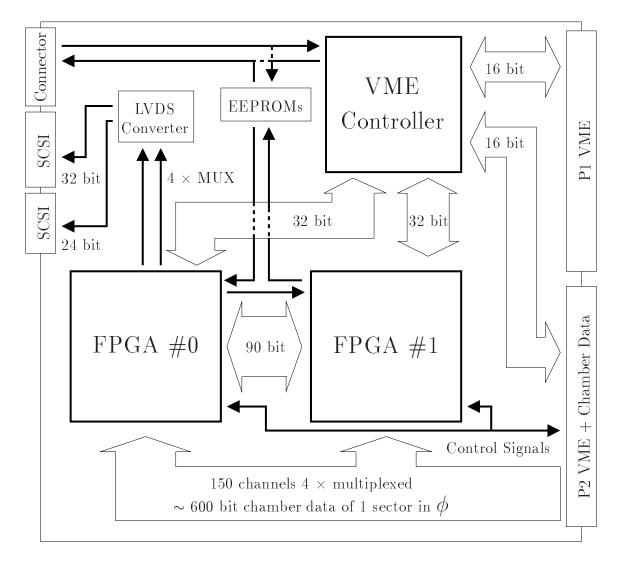

| 3.10 | CIP2000 trigger card                                            | 21 |

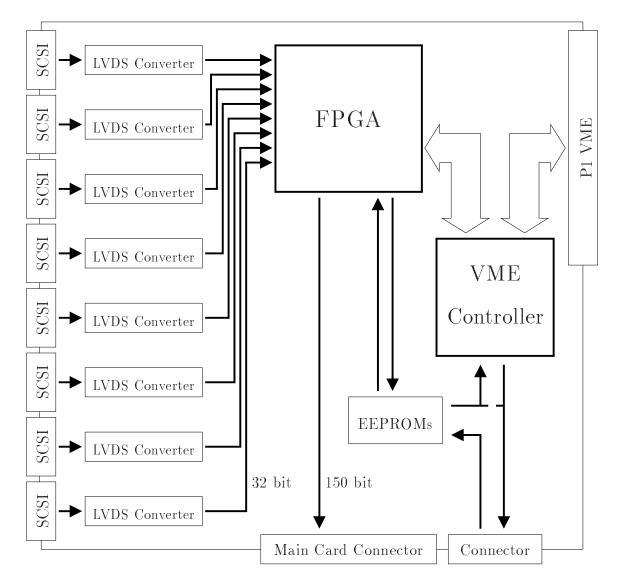

| 3.11 | CIP2000 sum card                                                | 22 |

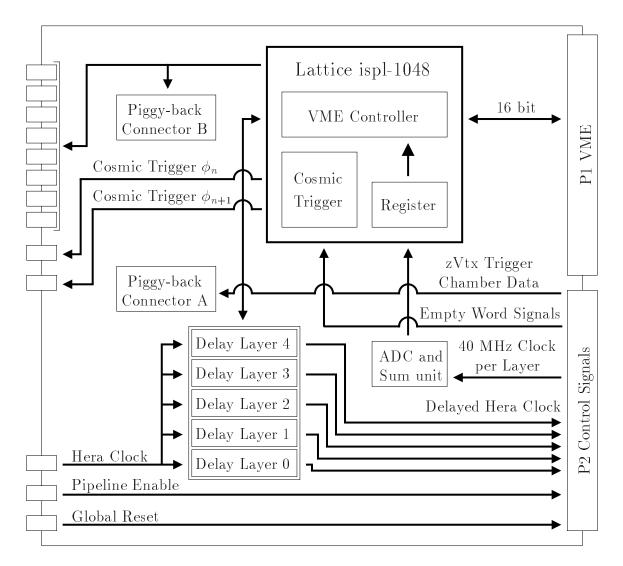

| 3.12 | CIP2000 control card                                            | 23 |

| 3.13 | Timing of the CIP2000 trigger                                   | 24 |

| 4.1  | CIP2000 trigger system control structure                        | 26 |

| 4.2  | Structure of a standard STC system                              | 27 |

| 4.3  | Trigger signal timing – L1 Keep, L2 Reject                      | 31 |

| 4.4  | Trigger signal timing – L1 Keep, L2 Keep, L3 Reject             | 32 |

| 4.5  | Trigger signal timing – L1 Keep, L2 Keep, L3 Keep               | 33 |

| 5.1  | CIP2000 trigger readout structure                               | 39 |

| 5.2  | CIP2000 trigger readout timing                                  | 40 |

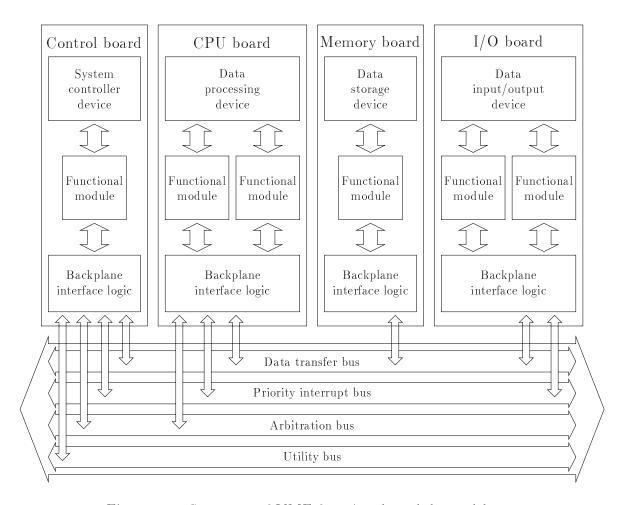

| 5.3  | Structure of VME functional modules and buses                                    | 42 |

|------|----------------------------------------------------------------------------------|----|

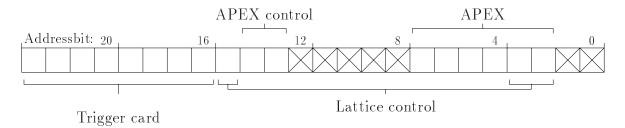

| 5.4  | Address mapping to the VME resources on the trigger cards                        | 44 |

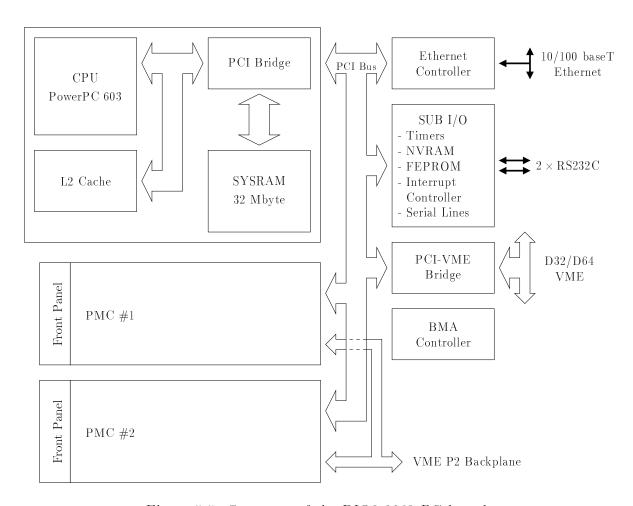

| 5.5  | Structure of the RIO2 8062 PC board                                              | 45 |

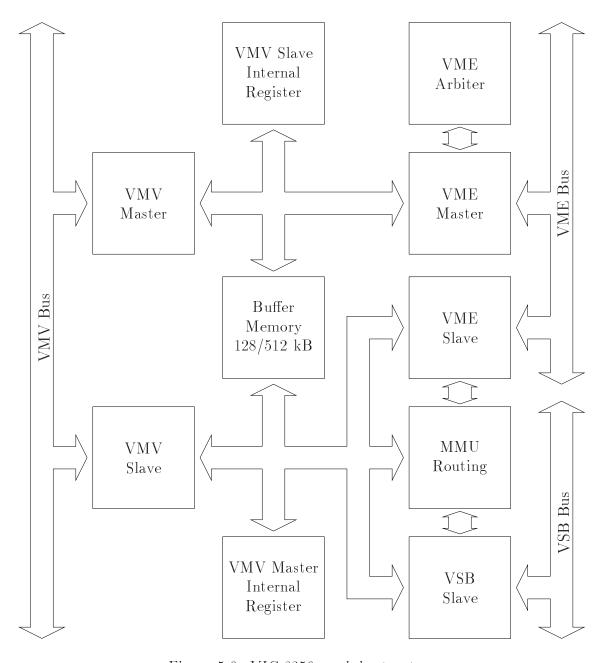

| 5.6  | VIC 8250 module structure                                                        | 48 |

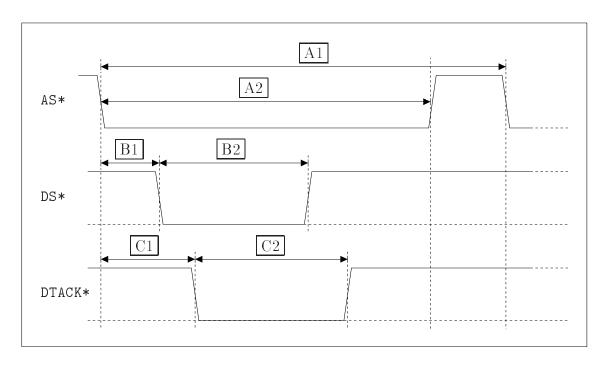

| 6.1  | Signal timing of a VME bus single cycle data transfer                            | 52 |

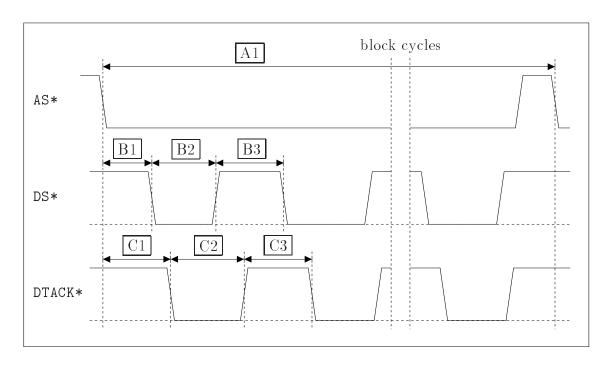

| 6.2  | Signal timing of a VME bus block data transfer                                   | 53 |

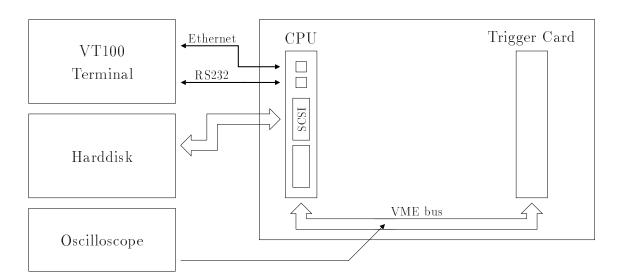

| 6.3  | Test system to examine the VME bus performance                                   | 53 |

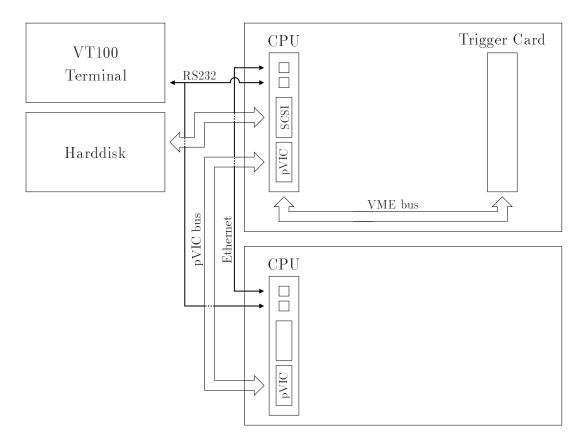

| 6.4  | Test system to examine the pVIC connection performance                           | 56 |

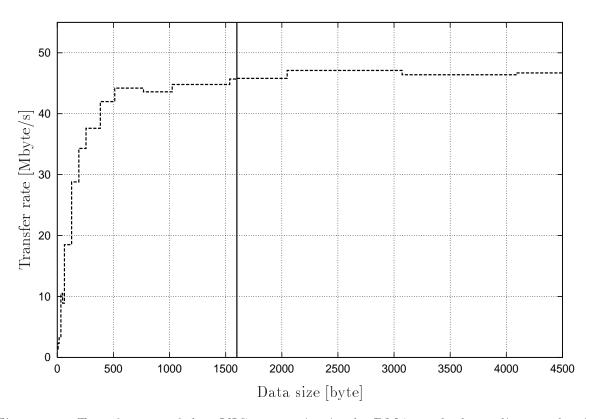

| 6.5  | Transfer rate of the pVIC connection in the DMA mode                             | 57 |

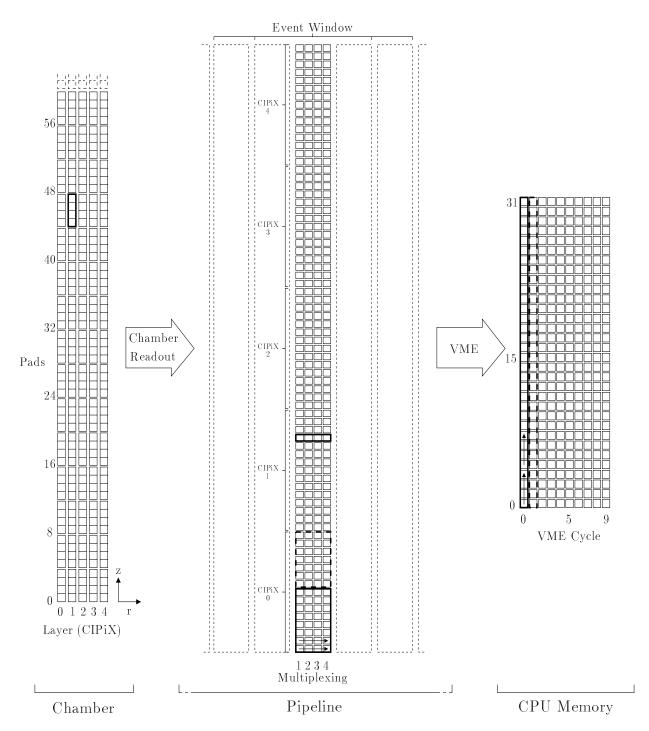

| 7.1  | Mapping of the chamber data on the CPU memory                                    | 59 |

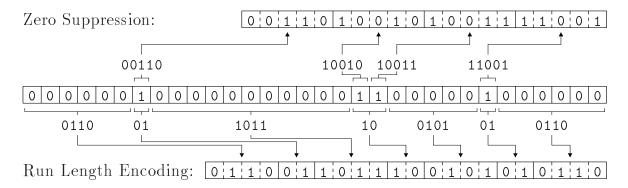

| 7.2  | Data reduction algorithms                                                        | 60 |

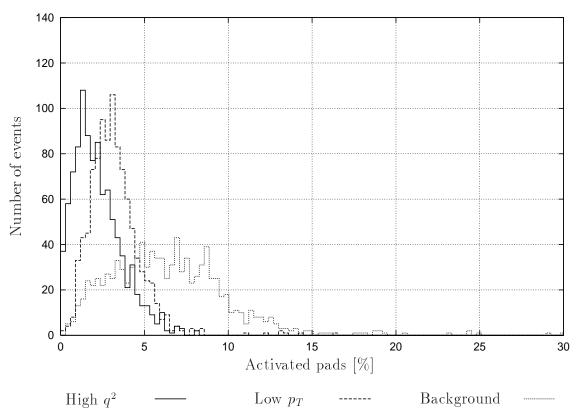

| 7.3  | Activated pads: different event types, no noise                                  | 62 |

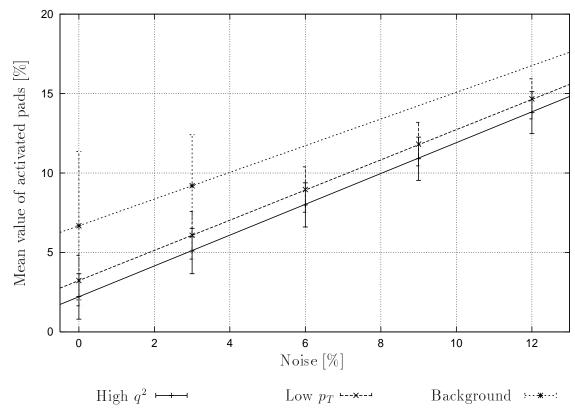

| 7.4  | Activated pads: noise dependence for mean value of activated pads                | 63 |

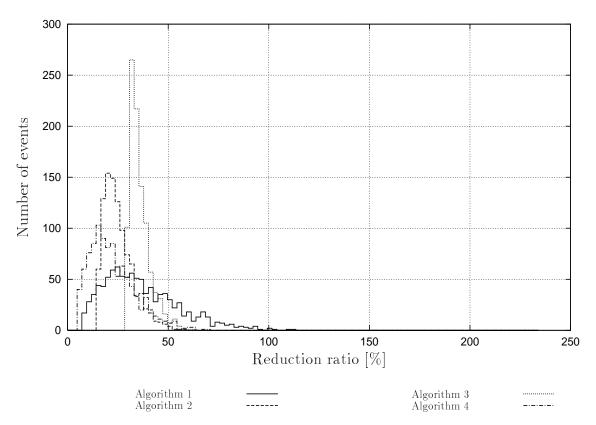

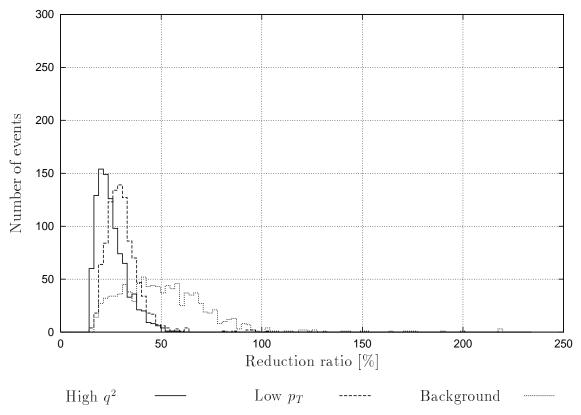

| 7.5  | Reduction ratio for different algorithms on high $q^2$ events, no noise          | 64 |

| 7.6  | Reduction ratio for different algorithms on low $p_T$ events, no noise           | 64 |

| 7.7  | Reduction ratio for different algorithms on background events, no noise          | 65 |

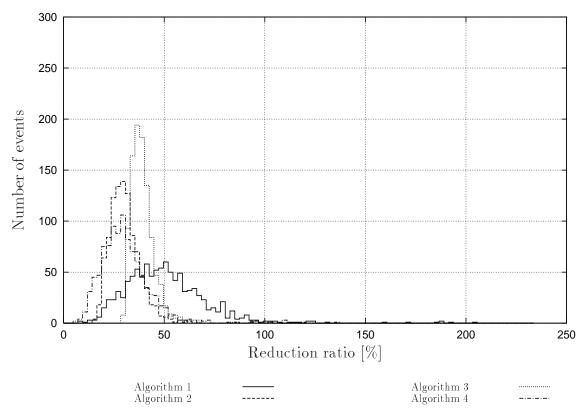

| 7.8  | Reduction ratio for algorithm 2 on different event types, no noise               | 65 |

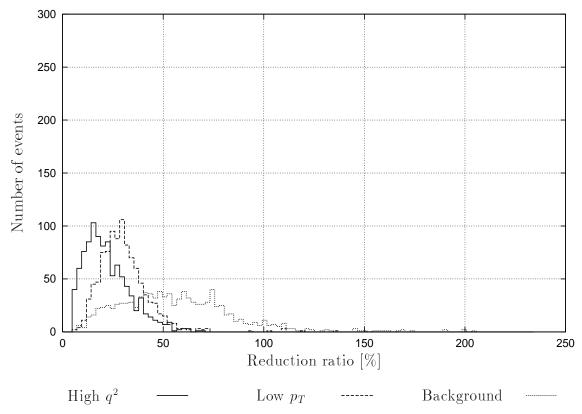

| 7.9  | Reduction ratio for algorithm 4 on different event types, no noise               | 66 |

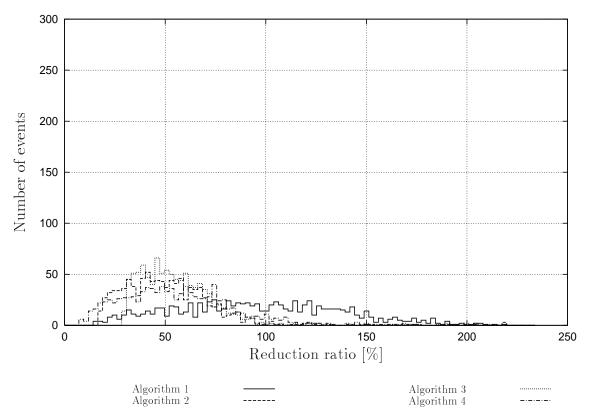

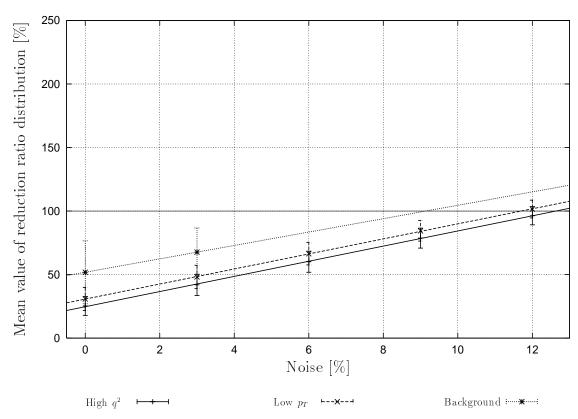

| 7.10 | Noise dependence of the reduction ratio for algorithm 2 on different event types | 66 |

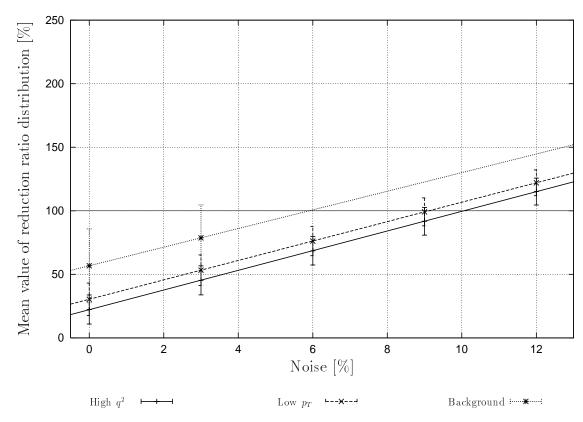

| 7.11 | Noise dependence of the reduction ratio for algorithm 4 on different event types | 67 |

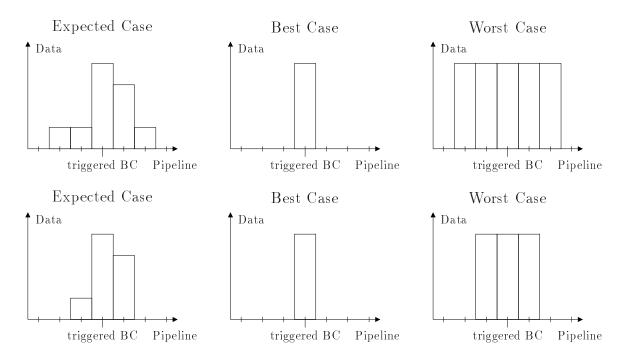

| 7.12 | Models for event data in the pipeline                                            | 68 |

# List of Tables

| 3.1 | Pad geometry of the new CIP2000 chamber                                                                   | 16 |

|-----|-----------------------------------------------------------------------------------------------------------|----|

| 4.1 | Trigger signals                                                                                           | 28 |

| 5.1 | Assumed duration of the horizontal and vertical readout                                                   | 41 |

| 6.1 | Measured timing parameters of VME bus data transfers: single cycle mode                                   | 54 |

| 6.2 | Measured timing parameters of VME bus data transfers: block mode                                          | 54 |

| 6.3 | Measured VME bus data transfer performance                                                                | 55 |

| 6.4 | Transfer rate of the pVIC connection in the DMA mode                                                      | 57 |

| 7.1 | Run length encoding (RLE) algorithms                                                                      | 61 |

| 7.2 | Mean value and width of distribution of activated pads: different event types, no noise                   | 62 |

| 7.3 | Reduction ratio and width of the distribution for different algorithms on different event types, no noise | 63 |

| 7.4 | Reduction ratio for different models of event distribution in the pipeline for algorithm 2                | 68 |

| 7.5 | Reduction ratio for different models of event distribution in the pipeline for algorithm 4                | 69 |

# Chapter 1

### Introduction

The HERA (Hadron-Elektron-Ring-Anlage) particle collider at DESY in Hamburg (Germany) is operating since May 1992. An upgrade for HERA is planned for 2000/2001. In the upgrade the size of the focus of the beams is reduced leading to a higher luminosity. The detectors have to be adapted to the new situation. A bigger number of background events is expected. A new fast trigger is developed to examine and suppress the background events.

The new trigger system is called CIP2000 trigger system. The trigger system uses the pad information of five cylindrical chambers to find and count tracks originating from the beam axis. The number of tracks originating from different parts of the beam axis are summed up to a z-vertex histogram. The structure of the z-vertex histogram makes it possible to detect background events. The trigger system uses FPGAs (Field Programmable Gate Array) mounted on trigger cards to implement the trigger algorithm. The chamber data is stored in pipelines situated in the FPGAs. CPUs read out the data via a VME bus and a pVIC connection.

The aim of this diploma thesis is to develop the control system and the readout system for the new trigger. The communication of the different CPUs and the new designed trigger cards is tested in a test system. The pVIC bus between the different CPUs is examined. Different data reduction algorithms to reduce the size of the events read out from the pipelines are simulated. The communication of the different parts of the whole CIP2000 trigger system is designed. The connection and communication of the STC (Subsystem Trigger Control) system and the CIP2000 trigger system is specified and some parts of the communication are tested.

- Chapter 2 gives an introduction to the HERA particle collider, the H1 detector and the upgrade for HERA 2000.

- Chapter 3 gives an overview of the CIP 2000 trigger system and the hardware components used in the system.

- Chapter 4 explains the structure of the trigger control system and the system to control the whole CIP2000 system.

- Chapter 5 gives an overview of the planned readout system of the CIP2000 trigger and its hardware components.

- Chapter 6 gives an overview of tests made with the readout test system.

- Chapter 7 shows the results of simulations of the data reduction on the raw data of the CIP2000 trigger readout system.

# Chapter 2

### HERA and the H1 detector

#### 2.1 The HERA machine

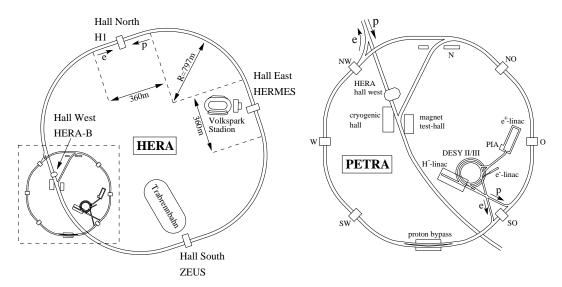

Two independent machines reside in the 6.3 km long tunnel some 15 m below the surface. One is an electron (alternatively positron) storage ring, which accelerates the particles from an initial 14 GeV to 30 GeV. The proton machine starts with initial 40 GeV accelerating the protons to 920 GeV before a collision with the electrons or a target is forced. The energy of the proton beam is limited by the strength of the magnets needed to bend the beam on its orbit. The HERA proton ring consists of superconducting magnets which produce a field of 4.6 T. Figure 2.1 gives an overview of HERA and its injector chains. The particles are packed into a maximum of 210 bunches, with a bunch crossing distance of only 96 ns. Not all of the bunches are filled with particles. The bunch crossings with no interactions are used to determine the background situation. The currents of the beams have been successfully increased in the last years. At the moment four experiments use the HERA storage rings. H1 and ZEUS are built around two interaction regions of the storage rings. The HERMES detector records the scattering of the polarized electron

Figure 2.1: The HERA storage ring with its pre-accelerators PETRA, DESY and Linacs

beam on polarized gas targets. The HERA-B experiment is built to measure CP violation in  $B^0 - \bar{B}^0$  systems generated by collisions of beam protons with a wire target.

#### 2.2 The H1 detector

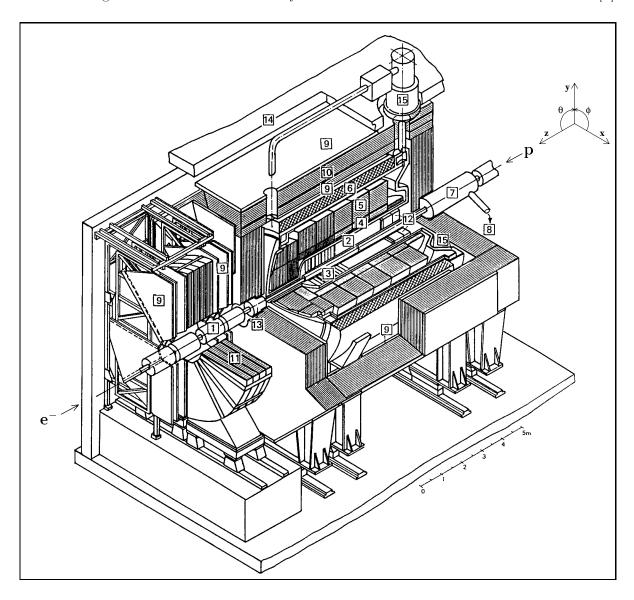

The H1 detector, located at the north interaction region of HERA is shown in Figure 2.2 also including the standard coordinate system. The detector is described in detail in [1].

Figure 2.2: Overview of the H1 detector. 1 Beam pipe and beam magnets, 2 Central tracker, 3 Forward tracker, 4 Electromagnetic LAr calorimeter, 5 Hadronic LAr calorimeter, 6 Superconducting coil, 7 Compensating magnet, 8 Helium supply for 7, 9 Muon chambers, 10 Instrumented iron yoke, 11 Forward muon toroid, 12 Backward calorimeter, 13 PLUG calorimeter, 14 Concrete shielding, 15 LAr cryostat

The proton direction (positive z direction) is called the forward direction. The electron direction (negative z direction) is referred as the backward direction. Starting from the interaction vertex the detector consists of a central and a forward tracking system, each containing different layers of drift chambers and trigger proportional chambers. A liquid argon calorimeter surrounds the trackers. It is subdivided into an electromagnetic and a hadronic section. A superconducting cylindrical coil with a diameter of 6 m provides the analysing magnetic field of 1.15 T. The iron return yoke of the magnet is laminated and filled with limited streamer tubes. Hadronic energy leaking out of the back of the calorimeter is registered there. Muon identification benefits from additional chambers inside and outside of the iron. Muon tracks in the forward direction are analysed in a toroidal magnet sandwiched between drift chambers. Remaining holes in the liquid argon calorimeter are closed with warm calorimeters, a silicon-copper plug at very forward angles, a lead-scintillator calorimeter and lastly electron tagger in very backward regions. Two scintillator walls in the backward direction are installed to recognize background produced by the proton beam upstream of the H1 detector. Different parts of the H1 detector are grouped in so called subsystems. The subsystems are responsible for the readout of the subsystems detectors to the central DAQ. Several subsystems provide trigger systems for the different levels of the H1 trigger system.

#### 2.2.1 H1 trigger system

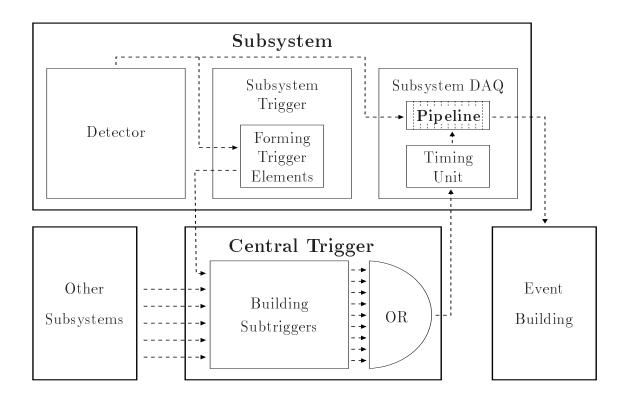

Due to the low cross sections of ep interactions, the rate of genuine events is much smaller than the rates for background processes. Typical background sources are collisions between beam protons and rest gas in the vacuum pipes, scattering of off-momentum protons or electrons on beam apertures, collisions of protons between bunches (satellites) due to incorrect pre-acceleration or scattered synchrotron radiation from the electron beam. The different background sources are described in detail in Section 3.1. The HERA experiments need to rely on sophisticated triggering systems, selecting the good events very quickly. The trigger of the H1 detector is divided into four levels. Figure 2.3 shows an

| t        | 0.0 2.3       | $\mu$ s 20                            | $\mu$ s (planed) < 80 | $0 \ \mu \mathrm{s}$ ca.100 ms |

|----------|---------------|---------------------------------------|-----------------------|--------------------------------|

|          | Level 1       | Level 2                               | Level 3               | Level 4                        |

| Output   | 1 kHz         | 100 Hz - 200 Hz<br>(limited to 50 Hz) | 50 Hz                 | 5 Hz                           |

| Action   | Stop pipeline | Start readout                         | Start eventbuilding   | Data logging                   |

| Hardware | Subsystems    | Topological trigger                   | PowerPC processors    | Power PC farm                  |

Figure 2.3: H1 trigger levels. The trigger of the H1 detector is divided into four levels. The first and second level systems are phase-locked to the HERA accelerator clock. The further trigger levels run asynchronously to the HERA clock. The L2 trigger output rate is limited to 50 Hz because no L3 trigger is implemented at the moment.

overview of the different trigger levels. A description of the H1 trigger system can be found in [1, 2].

The first and second level systems (L1 and L2) are phase-locked to the HERA accelerator clock of 10.4 MHz. The L1 system provides a trigger decision for each bunch crossing after 2.3  $\mu$ s without causing dead time. Pipelines in the different subsystems store the data for this period. Every L1 subsytem generates trigger information coded in bit pattern of a multiple of 8 bits. These bit patterns are called trigger elements and contain special information of the event. With Boolean decisions subtriggers are formed from the different subsystem trigger elements in the central trigger system. The central trigger system merges all the trigger informations of the different subsystems and the different levels. If one subtrigger comes to a positive decision the L1 Keep signal is sent to the subsystems and stops the pipelines. Figure 2.4 shows the principle of pipelining and the calculation of the trigger decision. All signals used until this point are synchronous to the HERA Clock. These signals are called fast signals. After the L1 trigger decision the asynchronous part of the trigger and the readout system begins. Signals used in the asynchronous communication are called slow signals.

The L2 trigger system decision is presently derived from a combination of two independent hardware systems within 20  $\mu$ s of the preceding L1 Keep signal, allowing sufficient time for transmission of trigger information and computation of the L2 trigger response. The L2 trigger output rate is at the moment limited to 50 Hz because no L3 trigger is implemented

Figure 2.4: Principle of pipelining in H1 subsystems. The chamber information is stored in a pipeline to avoid dead time in the first level of the trigger system. After a positive trigger decision the corresponding event information is read out from the pipelines.

yet. The future L3 system will be a software trigger. The L4 stage of the trigger system cuts on full event quantities and manages the data logging and a preprocessing of the event reconstruction. Only after the data logging a full reconstruction of the events is performed.

#### 2.2.2 H1 readout system

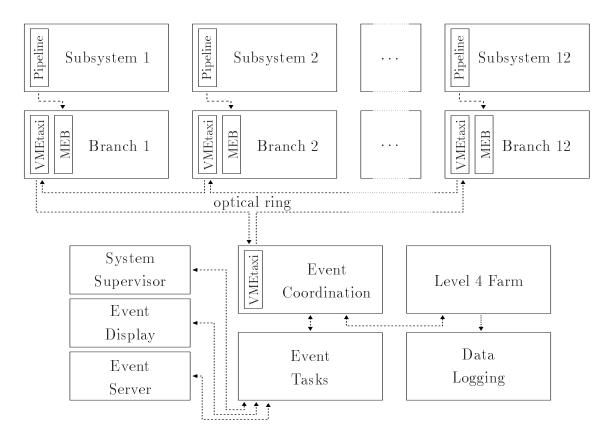

An overview of the H1 DAQ system can be found in [1, 2]. A total of over a quarter of a million analogue channels are read out and digitized, resulting in some 3 Mbyte of raw digitized information for a triggered event. Various levels of hardware triggering, software filtering and digital compression reduce the event size to between 50 Kbyte and 100 Kbyte. Figure 2.5 shows an overview of the H1 detector readout system. The whole data is passed from the subsystems via an optical readout ring to the event building unit where the data is examined in different stages and written on tape. For the readout the individual subsystems use VME bus crates each containing a readout controller, a memory buffer and a fibre optic link to a coordinating event manager. The event manager coordinates the data flow between the optical readout ring, systems observing the read

Figure 2.5: Principle of the H1 detector readout. The different subsystems are connected to the main event building via an optical ring. The event coordination collects the full event data. It is processed in the event task unit. After processing the data it is send to the data logging. The Level 4 farm does first online reconstructions on the read out data.

out data and the process of data logging. The different parts of the optical link are called branches. Some subsystems share the same optical branch. The VME bus and VSB bus are used as the main standards in the H1 detector readout. VMEtaxi [3] cards are used to drive the optical ring connecting the subdetector VME crates to the event building.

#### 2.3 The H1 upgrade for HERA 2000

The investigations of rare processes at the limits of the kinematically accessible range at HERA requires high luminosity. For instance in the very high  $Q^2$  region ep collision experiments allow to give the best limits compared to other accelerators on hypothetic particle states, which have both leptonic and quark quantum numbers ("Leptoquarks"). The goal is to increase the luminosity of HERA by a factor of 5 to about  $7.4 \times 10^{31}$  cm<sup>-2</sup>s<sup>-1</sup>, which will lead to an annual integrated lumionsity of 150 pb<sup>-1</sup>. For further information on the physics goals of the upgrade see [4].

The higher luminosity will mainly be achieved by a stronger focusing of both beams in the experimental areas. This requires the installation of three new superconducting magnets inside the H1 detector, one in the forward and two in the backward hemisphere. Each of them is equipped with an independant cooling system. To gain enough space for these magnets and to adapt to the new beam geometry, significant changes to the inner part of the H1 detector are necessary. First of all the vacuum beam pipe (made from Aluminium - Beryllium alloy) will have an elliptical shape corresponding to the synchrotron radiation envelope and allowing to install at least part of the CST as close as possible to the interaction region. The inner hole of the SPACAL needs to be enlarged to make room for the new magnets.

We have to assume, that also the beam related background will increase with higher luminosity, although it is very difficult to predict quantitatively how much. For this reason the CIP2000 upgrade project replaces the CIP and CIZ chambers by a new 5 layer MWPC. A new fast trigger system based on the cathode pad signals of this new chamber will be able to identify uniquely upstream proton background and provide a strongly improved rejection capability for those events. Electron beam induced photon background will be suppressed due to the new five layer chambers instead of only two in the old system.

Although the main goal of the upgrade is the study of the very high  $Q^2$  region with its low physics event rates, the access to low  $p_t$  physics, mainly for measurements using heavy quarks is still interesting and has not yet been fully exploited with the present system. ep events with only light quarks in the final states are the main background to these events. Using the present trigger system heavy quark events could only be accessed with good efficiency by increasing the overall bandwidth of the data taking system, which would be prohibitive. Therefore a Fast Drift Chamber Track Trigger (FTT) will be built to find tracks in the CJC detectors. Event signatures indicating heavy quark or other interesting final states will be calculated with the FTT in trigger level 2 and 3, thus allowing to selectively acquire these events.

In addition the calorimeter jet trigger will be adjusted to a higher granularity. The luminosity system will have to be adapted to the new luminosity situation. Detectors like the Forward Silicon Tracker (FST), Backward Silicon Tracker (BST), Forward Track Detectors

tor (FTD), Forward Neutron Calorimeter (FNC), Forward Proton Spectrometer (FPS) or Backward Proportional Chamber (BPC) will substitute or complement old detectors or are totally new developments. A new high performance processor farm will be able to fully reconstruct the event data online, allowing more specific physics cuts and monitoring tasks to run on the data before storage.

# Chapter 3

# The CIP2000 trigger system

#### 3.1 Motivation

Due to the higher luminosity of the HERA 2000 upgrade also more background events are expected. Both the electron and the proton beam can be the source of background events. Protons can collide with residual gas particles. In addition they can leave the nominal orbit and collide with the beam pipe or e.g. the magnets. Bad pre-acceleration can lead to protons outside the correct bunch timing (satellite bunches). The satellite bunches can too collide with residual gas particles or with e.g. the beam pipe. The proton generated background results in event signatures with the interaction vertex on the beam axis but at a different position in the z direction than the nominal vertex region. The electron beam creates synchrotron radiation. The photons from this radiation can produce pairs of particles by photon conversion. These particles are absorbed in the chambers very fast due to their low energy. Mostly no tracks can be reconstructed in this event signature. These events are rejected automatically because of the five layers of the CIP2000 chamber. The CIP 2000 trigger builds coincidences of pads in the five layered CIP 2000 chamber and defines tracks of particles going through the detector. Tracks originating from the beam axis of the H1 detector are counted and summed up in different regions (size: 20 cm) of the x-axis separatly. The resulting numbers form a histogram called z-vertex histogram. It reaches from the forward direction nearly through the whole main detector up to the SPACAL. From this information proton-upstream background events can be easily identified. The events can be rejected or specially examined.

Simulations have been done to examine the background rejection of the CIP2000 trigger [5]. The geometrical constraints for the CIP2000 chamber geometry have been investigated [6] and a hardware trigger algorithm has been developed and simulated [7]. The loss for physics events is less than 1% whereas background from outside the nominal interaction region with lots of activity in the detector is rejected with an efficiency of more than 95%.

The old CIP chambers and the CIZ chamber will be moved out of the experiment to provide space for the new five layered CIP2000 chamber. The forward MWPC system will be taken out but the old MWPC trigger will still exist as it is, besides not providing the forward region. It uses the two inner layers of the new CIP2000 chamber and the

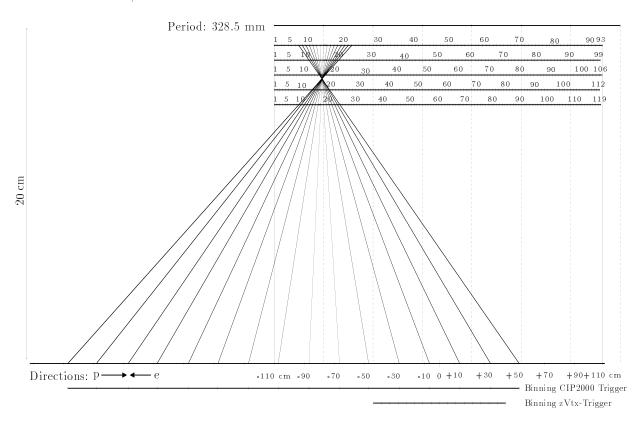

COP chamber to build a z-vertex histogram similar to the histogram provided by the CIP2000 trigger. The zVtx trigger z-vertex histogram covers a smaller region in z but has a better resolution (bin size: 5.49 cm). The zVtx trigger examines the region of the nominal vertex but does not provide informations of other regions in the z direction. The binning of the z-vertex histogram for the zVtx and the CIP2000 trigger can be found in Figure 3.5.

#### 3.2 Trigger algorithm

The trigger algorithm of the CIP2000 trigger calculates a z-vertex histogram to determine the ratio of tracks originating from the *ep* interaction point to tracks originating from very forward or backward regions of the detector. This information is coded in the trigger elements of the CIP2000 trigger and sent to the central trigger unit.

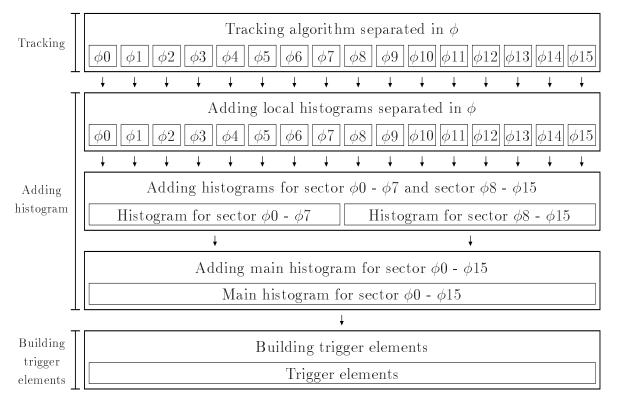

To make the implementation of the trigger algorithm most efficient and fast the main tasks are separated into small steps which can be calculated in parallel. The possibility for a separation results mostly from the geometry of the chambers. With assuming that all tracks measured in the chambers are coming from the beam axis of the H1 detector the algorithm can be separated in  $\phi$ . The local z-vertex histograms calculated in every sector in  $\phi$  can be summed up to a total z-vertex histogram for the whole chamber. A "projective geometry" was chosen for the chamber geometry in order to allow to separate the algorithm in the z direction. This method is explained in detail in Section 3.3. These possibilities for the separation of the trigger algorithm leads to an implementation concept with the following three main parts, visualized in Figure 3.2:

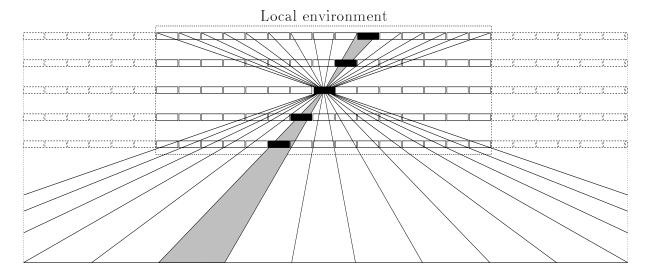

Tracking: To find all the tracks in a given sector in  $\phi$  the algorithm is subdivided into smaller parts. For every pad in the middle layer called central pad a local environment is defined. An example of a local environment is shown in Figure 3.1. The required binning of the z-vertex histogram defines how the algorithm searches for tracks in the local environment. The binning can be shifted in parts of one bin width by defining an offset in the definition of the local environment. Figure 3.1 shows how the tracks are defined. Because of the projective geometry of the chambers the definition of the tracks in the local environment is independent of the z position of the central pad. For the local environment of every pad in the middle layer it is memorized how many tracks originate from each bin. This is achieved by simple comparison of the bit pattern. The information is called the hit list. The algorithm is executed in parallel for every central pad and every sector in  $\phi$ .

Adding the main histogram: The hit lists of all central pads in one sector in  $\phi$  are added up. The result is a local z-vertex histogram for every sector in  $\phi$ . After all local histograms are added up the main z-vertex histogram for the whole chamber is available.

Building trigger elements: Trigger elements (16 bit) are built from the main z-vertex histogram. The detailed definition of the trigger elements is not yet defined.

Figure 3.1: Definition of a local environment. The possible tracks are defined in the local environment. Because of the projective geometry of the chambers the definition of the tracks in the local environment is independent of the z position of the central pad. The tracks are recognized by simple comparison of the bit pattern.

Figure 3.2: Overview of the CIP2000 trigger algorithm. The main tasks of the trigger algorithm can be separated in small steps which can be calculated in parallel. The possibility for a separation results mostly from the geometry of the chambers.

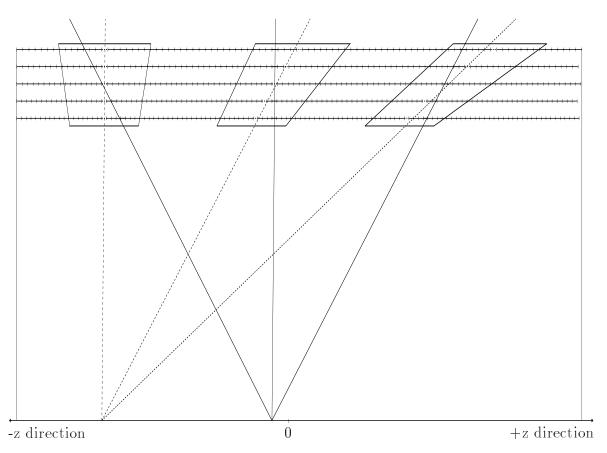

#### 3.3 Projective geometry

To make the tracking algorithm easier a projective geometry was chosen. Figure 3.3 demonstrates what a projective geometry means and defines a coordinate system. The projective geometry means that the pad size in z of one layer is proportional to the radius of the layer. The tracking algorithm searches for tracks in a local environment like it is shown in Section 3.2. Every pad in a layer gets its pad number by counting the pads from the -z end of the chamber on. Fifteen consecutive pads of each layer with the same pad number in each layer form a local environment. The different local environments are tilted against each other. If one searches for a track in the environment originating from a given point on the z-axis one has to look for a special bit pattern. The projective geometry has the consequence that all possible tracks originating from the given point on the z-axis have the same bit pattern in the different local environments. The algorithm does not have to know the z position of the local environment to find a track originating from a special point on the z-axis. This means that all units running the tracking algorithm can run with the same setup.

Figure 3.3: Projective geometry. The pad size of one layer is proportional to the radius of the layer. The local environment of a pad in the central layer is tilted along the z direction the way that every track originating from one point on the z axis makes the same bit pattern in the local environment of any central layer pad.

### 3.4 Trigger system implementation

The CIP2000 trigger system hardware implementation consists of three main parts:

- CIP2000 chamber (5 layers) and chamber readout

- Trigger system and STC (Subsystem Trigger Control) system

- Trigger readout system

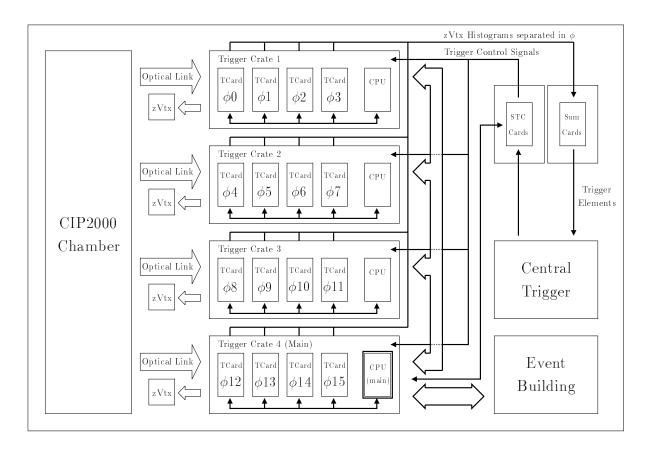

Figure 3.4 shows an overview of the whole system. The CIP2000 chamber consists of 5 cylindrical layers. Mounted directly on the chamber there is electronics, which amplifies, discriminates and multiplexes the signals before they are sent via an optical fibre to the trigger crates in the electronic trailor. FPGAs (Field Programmable Gate Arrays) on trigger cards in the trigger crates run the trigger algorithm in several stages and store the chamber information. The trigger elements are calculated in FPGAs on sum cards and

Figure 3.4: The CIP2000 chamber consists of 5 cylindrical layers. On chamber chips amplify, discriminate and multiplex the signals before they are sent via optical fibres to the trigger crates. FPGAs on trigger cards run the trigger algorithm and store the chamber data. The trigger elements are built on sum cards. Trigger CPUs read out the chamber data, compress the information and send it to the main event building. The STC system manages the communication between the central trigger unit and the CIP2000 system.

are sent to the central trigger unit. CPUs read out the chamber informations, compress the data and send it to the main event building. The STC system manages the communication between the central trigger unit and the CIP2000 trigger system.

FPGAs are an essential part of the CIP2000 trigger system. Investigations have been made if ASICs, DSPs or FPGAs are best suited for managing the tasks of running the trigger algorithm and storing the chamber data. The FPGAs contain freely programmable logical units thus combine a performance in speed and parallelism like a digital ASIC with the flexibility of a multiprocessor like a DSP. The FPGAs used in the system have a random access memory built into the chip to store the chamber data. It turned out that FPGAs are best suited for the requirements of the CIP2000 trigger system.

#### 3.4.1 Chamber geometry

The chamber of the CIP2000 trigger consists of 5 cylindrical layers. Each layer is divided in 16 Sectors in  $\phi$  and about 120 equidistant pads in the z direction. A projective geometry was chosen to make the tracking algorithm easier. The characteristic of this geometry is illustrated in Section 3.3. Table 3.1 shows the detailed sizes of the pads in the different layers. The chamber has an acceptance in  $\Theta$  of  $10^{\circ}$  -  $170^{\circ}$ . Figure 3.5 shows a side view of one sector in  $\phi$  of the new CIP2000 chambers.

Figure 3.5: Side view of one sector in  $\phi$  of the new CIP2000 chamber. The binning of the CIP2000 trigger histogram in comparison to the histogram of the zVtx trigger is shown. By changing the program of the trigger algorithm on the FPGAs on the trigger cards the bins can be shifted in forward and backward direction in steps of  $\sim$ 20 cm.

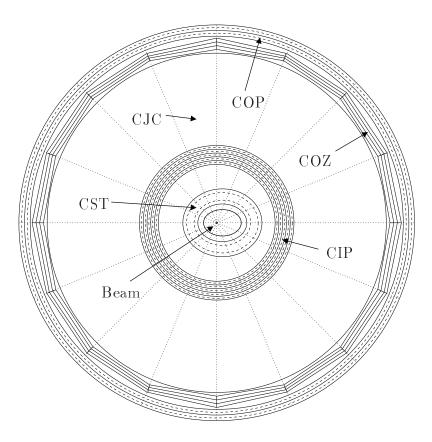

The figure shows the binning of the CIP2000 trigger histogram in comparison to the histogram of the zVtx trigger. By changing the program of the trigger algorithm on the FPGAs on the trigger cards the bins can be shifted in forward and backward direction in steps of ~20 cm. Figure 3.6 shows a front view of the new CIP2000 chambers with a part of the surrounding detector.

Figure 3.6: Front view of the CIP2000 chamber with the surrounding detector.

| Layer | Radius[mm] | Pad length[mm] | Number of Pads |

|-------|------------|----------------|----------------|

| 0     | 157        | 18.250         | 119            |

| 1     | 166        | 19.323         | 112            |

| 2     | 175        | 20.531         | 106            |

| 3     | 184        | 21.900         | 99             |

| 4     | 193        | 23.464         | 93             |

Table 3.1: Pad geometry of the new CIP2000 chamber

#### 3.4.2 Chamber readout

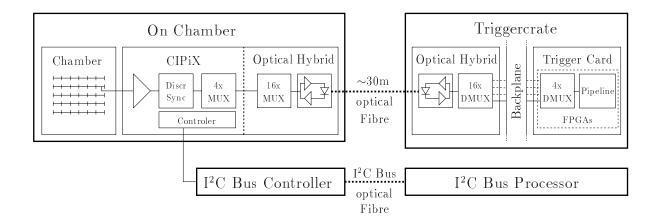

The signals of the chamber pads are amplified, discriminated and synchronized to the accelerator bunch crossing clock (Hera Clock) by an ASIC called CIPiX. Every CIPiX has 64 channels and is connected to 60 pads in one layer and one sector in  $\phi$ . The whole system uses 160 CIPiX. The digitized data is multiplexed 4 times on the CIPiX chip. The chips can be controlled by a processor via an optical link using the I<sup>2</sup>C standard [8]. The modes of the preamplifier, shaper, discriminator and the multiplexing can be set. A test pulse generator can be used to test the readout chain. More information on the CIPiX chip can be found in [9].

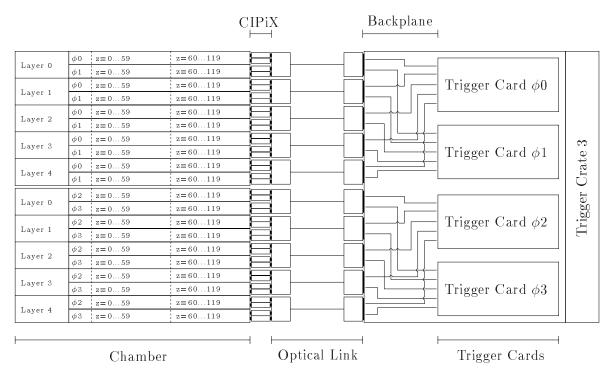

The digitized data of four CIPiX chips is collected in one optical hybrid. Here the data is again multiplexed 16 times and sent via an optical fibre to the optical hybrids in the electronic trailor. Control signals like the HERA clock are sent from the electronic trailor to the chamber via the same link. The optical link operates at a rate of about 800 MHz. The optical hybrids in the electronic trailor are mounted on the back of the trigger crate backplanes. 10 of these optical hybrids provide the data of 4 sectors in  $\phi$ . The data is demultiplexed 16 times. The backplane sorts the signal lines and distributes the data to the trigger cards. Every trigger card needs the data of all layers in one sector of  $\phi$ . The FPGAs on the trigger cards demultiplex the data 4 times and store the data in pipelines. The same FPGAs run the trigger algorithm. Figure 3.7 shows the readout chain of the CIP2000 chamber. Figure 3.8 shows how the data is distributed in the CIP2000 chamber readout for 4 sectors in  $\phi$ .

Every layer has its own I<sup>2</sup>C bus ring connected to all CIPiX chips in a layer. The five busses are driven by a processor in the electronic trailor. This processor receives its comands from the main CIP2000 CPU in serial form.

Figure 3.7: Signal path of the CIP2000 chamber readout. The CIPiX chip amplifies and multiplexes the data 4 times. Again the data is multiplexed 16 times and converted in optical signals in the optical hybrid. The optical link operates at a rate of about 800 MHz. The optical hybrid on the back of the trigger crate backplane demultiplexes the data 16 times. The backplane sorts the signals and distributes the data to the trigger cards. The FPGAs on the trigger cards demultiplex the data 4 times and store the data in pipelines.

Figure 3.8: Overview of the CIP2000 chamber readout for 4 sectors in  $\phi$ . Two CIPiX chips amplify and multiplex the data of one layer and one sector in  $\phi$ . The data of four CIPiX chips is multiplexed and converted in optical signals in one optical hybrid. The optical hybrid on the back of the trigger crate backplane demultiplexes the data. The backplane sorts the signals and distributes them to the trigger cards. Every trigger card needs the data of all layers in one sector of  $\phi$ .

#### 3.4.3 Trigger system hardware

Information about the CIP2000 trigger system and the hardware components can be found in [10]. The CIP2000 trigger system is built following the structure of the trigger algorithm with a maximum of flexibility in adapting to possible new modifications of the algorithm. Figure 3.9 shows an overview of the CIP2000 trigger system structure. The trigger system consists of four trigger crates and additional crates housing the STC system and the sum cards to add the histograms of the different sectors in  $\phi$ . In every trigger crate there are four trigger cards, two control cards and a CPU board mounted on the front side of the backplane. The CPU manages the chamber readout via the VME bus integrated in the J1 and J2 backplane of the trigger crates. Ten optical receiver cards are mounted on the back of the J2 backplane. The backplane sorts the signals of the chamber and distributes the signals to the different trigger cards. The control cards receive control signals from the STC system and deliver the signals to the trigger cards via the backplane.

The parallelism of the trigger algorithm determines the structure of the trigger system. Every trigger card is assigned to one sector in  $\phi$ . The trigger card receives the 600 bit (120 pads  $\times$  5 layers) wide pattern of one sector in  $\phi$  four times multiplexed from the backplane. The main part of the trigger card are the two FPGAs running the tracking

algorithm. Each FPGA builds the histogram for one half of one sector in  $\phi$  and stores the chamber data in an integrated pipeline. The histogram is transferred to one of the FPGAs to build the local histogram of one sector in  $\phi$ . After the histograms are calculated they are sent to the pre-sum cards. The pre-sum cards add the histograms of 8 sectors in  $\phi$  and sends the result to the main-sum card. The main-sum card builds the main z-vertex histogram and calculates the trigger elements before they are sent to the central trigger unit.

Figure 3.9: CIP2000 trigger system structure. The trigger system consists of four trigger crates and crates housing the STC system and the sum cards to add the histograms of the different sectors in  $\phi$ . Every trigger card is assigned to one sector in  $\phi$ . The trigger card receives the chamber data of one sector in  $\phi$  four times multiplexed from the backplane. The local z-vertex histograms are calculated in the trigger cards and sent to the pre-sum cards. The pre-sum cards add the histograms and deliver each the histogram of the half chamber in  $\phi$  to the main-sum card. The main-sum card builds the main histogram and calculates the trigger elements to send them to the central trigger unit.

Figure 3.10 shows an overview of the trigger card. The main devices on the trigger cards are the two FPGAs APEX 20k400GCC/1 [11] with 652 pins from the company Altera. The FPGAs have an internal memory space to implement a pipeline for the chamber data and sufficient room to run the trigger algorithm. They are running at a frequency of 41.6 MHz. First the chamber data is four times demultiplexed. The hit list is generated in each FPGA containing the histogram information of the local environment of every central pad in the sector in  $\phi$  for the pads assigned to the FPGA. The local histogram is built in each FPGA 1 sends its local histogram consisting of 15 bins with numbers of the width of 6 bit (90 bit transfer between FPGAs) to the FPGA 0. The FPGA 0 adds both local histograms resulting in a histogram of 15 bins with 7 bit wide numbers. The data of the histogram is multiplexed four times and converted into differential LVDS (ANSI/TIA/EIA-644 LVDS, IEEE 1596.3)[12, 13] standard resulting in 32 bit data that is four times multiplexed.

The trigger card is connected to the pre-sum card via cables with SCSI connectors (68 pins). An additional SCSI connector (50 pins) can be used to transfer additional data calculated (e.g. integrated histograms) in the FPGA 0 to other parts of the CIP2000 system or even to other H1 subsystems. A VME [14] controller built in a Lattice ispL-1048 PLD [15, 16] manages the VME access to the trigger card. The pipelines and special registers in the FPGAs, control registers of the VME controller and EEPROMs containing the FPGA program can be read and written via the VME bus. VME D32/A24 access in single cycle and block mode are supported. Section 5.3.1 describes the VME bus in detail. The FPGAs can be programmed via an external connector, via the EEPROMS on the trigger card or via the VME bus. A JTAG (Joint Test Action Group) [17, 18] chain is implemented on the trigger card connecting the external connector, the EEPROMs and the FPGAs. The JTAG chain can test the connections between the devices and manages the programming of the FPGAs.

Figure 3.11 shows an overview of the sum cards. Two pre-sum cards and one main-sum card are planned. Both types of sum cards use one FPGA of the same type like the trigger cards. The pre-sum cards are connected to the trigger cards via eight cables with SCSI connectors. After the signals from the trigger cards are received on the pre-sum card they are converted back from LVDS standard. The FPGA demultiplexes the signals and adds up the histogram for eight sectors in  $\phi$ . The pre-sum cards send the histogram consisting of 15 bins with 10 bit wide numbers via the 150 bit wide link to the main-sum card. The main-sum card adds the main histogram resulting in a 15 bin wide histogram with numbers of the width of 11 bit and builds the trigger elements to send them to the central trigger unit. The sum cards have the same VME controller like the trigger cards to access registers on the FPGA and to programm the EEPROMS or the FPGA. The FPGA can be programmed via a JTAG chain like on the trigger cards.

Figure 3.12 shows an overview of the control cards. Its main task is to distribute the Hera clock signal, Pipeline Enable signal and a Global Reset signal to the trigger cards via the backplane and to distribute the Hera clock signal to the chamber electronics via the optical link. The Hera Clock signal can be delayed individually for every layer of the CIP2000 chamber. This is necessary to adjust the timing in the optical chamber readout. The delays can be set via the VME bus. The optical readout cards deliver a 40 MHz clock generated in the chamber electronics from the Hera Clock. These signals are received by

Figure 3.10: CIP2000 trigger card. The two FPGAs APEX 20k400GCC/1 from the company Altera have an internal memory space to implement a pipeline for the chamber data and sufficient room to run the trigger algorithm. First the chamber data is four times demultiplexed and stored in the pipeline. The hit list is generated in each FPGA. The local histogram is build in each FPGA and the FPGA 1 sends its local histogram (90 bit transfer between FPGAs) to the FPGA 0. The FPGA 0 adds both local histograms resulting in a histogram of 15 bins with numbers of the width of 7 bit. The data of the histogram is multiplexed four times and converted into differential LVDS standard. The trigger card is connected to the pre-sum card via cables with SCSI connectors. An additional SCSI connector can be used to transfer additional data calculated in the FPGA 0 to other parts of the CIP2000 system or even to other H1 subsystems.

the control card and the phase of the signals in different layers is examined and certain values are made available in registers. These registers can be read via the VME bus. The delays for the Hera clock can be adjusted depending on the values in the register. Certain chamber signals from the inner layers are also needed for the zVtx trigger of the old MWPC trigger system. These chamber data is made available in LVDS standard on

Figure 3.11: CIP2000 sum-card. There are two pre-sum cards and one main-sum card planned. Both types of sum cards have one FPGA of the same type like the trigger cards. The pre-sum cards are connected to the trigger cards via eight SCSI connectors and differential cables. After the signals from the trigger cards are received on the pre-sum card they are converted back from LVDS standard. The FPGA demultiplexes the signals and adds up the histogram for eight sectors in  $\phi$ . The pre-sum cards send the histogram consisting of 15 bins with numbers of the width of 10 bit via the 150 bit wide link to the main-sum card. The main-sum card adds the main histogram resulting in a 15 bin wide histogram with numbers of the width of 11 bit and builds the trigger elements to send them to the central trigger unit.

a piggy-back card (piggy-back A) mounted on the control card. Another piggy-back (piggy-back B) card mounted on the control card makes signals used on the control card available on LED displays. The same signals are made available on lemo connectors on the front side of the control card. A Lattice ispL-1048 PLD is used as a VME controller and for the implementation of a cosmic trigger. This cosmic trigger combines the pad

Figure 3.12: CIP2000 control card. The Hera Clock signal, the Pipeline Enable signal and the Global Reset signal are distributed by the control card via the backplane to the trigger card. The Hera Clock can be delayed individually for every layer of the CIP2000 chamber. The delays can be set via the VME bus. The optical chamber readout cards use a 40 MHz clock generated from the Hera clock. This clock signal from every chamber layer is received on the control card. The phase of the signals is compared and made available in a register. This register can be read via the VME bus. The delays of the Hera clock can be adjusted depending on the value of the register. Chamber signals from the inner layers are needed for the zVtx trigger of the MWPC trigger system. These chamber data is made available in LVDS standard on a piggy-back card (piggy-back A) mounted on the control card. A cosmic trigger is implemented on the control card providing information if one pad of every layer in one sector in  $\phi$  has been activated.

signals (Empty Word Signal) of different layers and generates a cosmic trigger signal for both sectors in  $\phi$  the control card is assigned to. The signal means that at least one pad of every layer has been activated.

#### 3.4.4 Timing

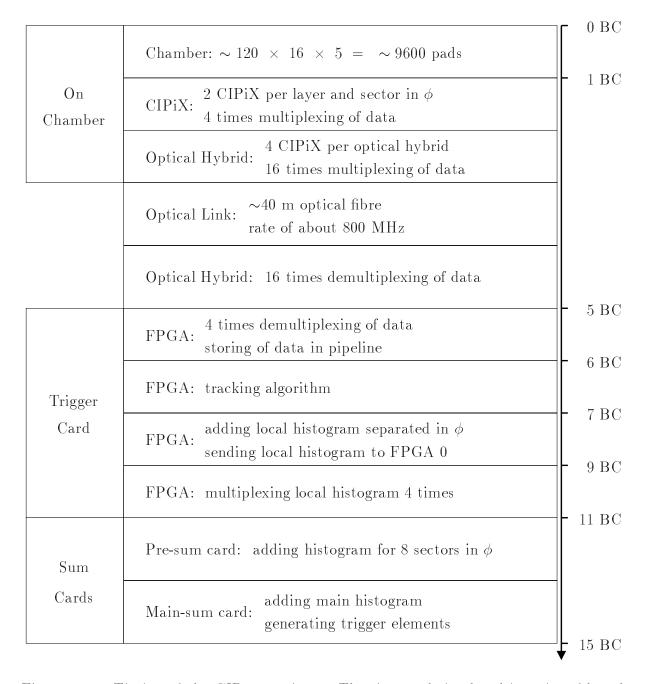

Figure 3.13 shows the timing behavior of the CIP2000 trigger as it is derived from simulations. The time scale is plotted in units of bunch crossings (1 BC = 96 ns). In comparison to other detectors the chamber readout is relatively slow because of the multiplexing of the data. By running the trigger algorithm in parallel on multiple devices the time for the tracking algorithm can be kept short. The summing of the histograms how ever ia a time consuming procedure.

Figure 3.13: Timing of the CIP2000 trigger. The time scale is plotted in units of bunch crossings (1 BC = 96 ns).

# Chapter 4

# The CIP2000 trigger control system

# 4.1 CIP2000 trigger system control structure

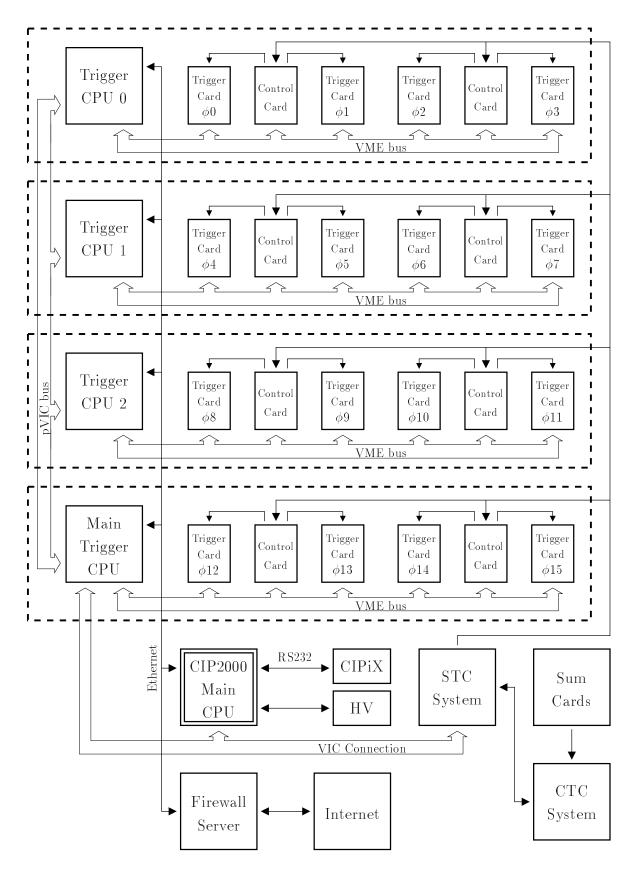

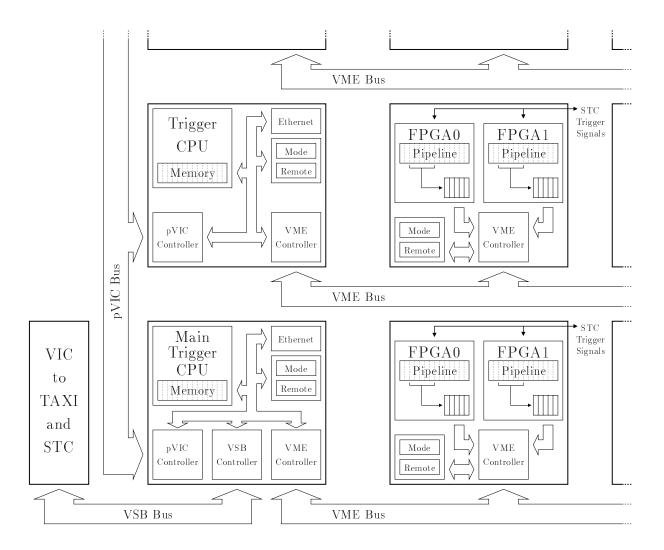

The control system for the CIP 2000 trigger has to connect and manage the communication between the different parts of the system. Three main parts have to be considered. The trigger and readout system, the high voltage system and the system to control the CIPiX chips. Figure 4.1 shows an overview of the planned system. The CIP2000 main CPU will run the main control system software that can be accessed via a firewall from the internet. A program displaying the status of the system can be run from the whole internet. A program to control the system can be run just on special machines or on a local computer in the control room. The CIP2000 main CPU is connected via a VIC (Vertical Interconnect) link to the Main Trigger CPU to control the trigger and readout system. A serial RS232 link to a processor communicating via the I<sup>2</sup>C protocol with the CIPiX chips manages the control and setup of the CIPiX chips. A connection to the high voltage system of the CIP2000 chamber will be established from the CIP2000 main CPU. An ethernet connection to all Trigger CPUs manages the booting of the CPUs. The trigger CPUs are connected via a pVIC (PCI Vertical Interconnect) link. The trigger CPUs communicate with the trigger cards via the VME bus. The STC system is connected to the main trigger CPU via a VIC link to manage interrupts from the STC system and to set and read special registers in the STC cards. All connections in the trigger and readout system will be explained in detail in Chapter 5. Fast signals like the Hera clock signal are transferred directly from the STC system to the control cards in the trigger crates. The control cards are connected to the trigger cards via the backplane to provide trigger control signals.

## 4.2 STC system

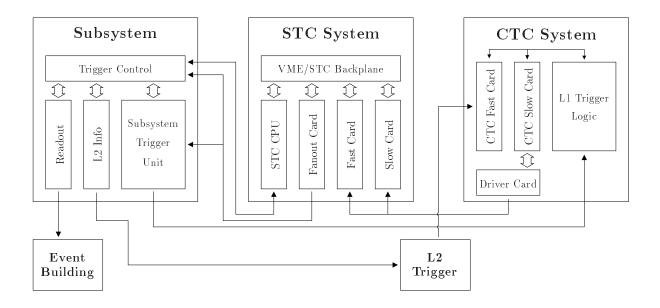

The STC (Subsytem Trigger Control) system manages the communication between the subsytems and the CTC (Central Trigger Control). It provides all necessary signals from the CTC and sends all needed signals back. A STC system consist of a STC Fast Card, a STC Slow Card, one or more STC Fanout Cards and a device that handles the VME

Figure 4.1: CIP2000 trigger system control structure

interrupts of the STC Slow Card. This device is normally a CPU that is housed in the STC crate. A Trigger Bit Card can be added to the STC sytem. The STC crate has a special VME/STC backplane. The backplane provides A24/D16 VME transfer. Figure 4.2 shows an overview of the connections between the different parts of the STC system and the CTC system. The subsystem trigger unit builds trigger elements from the detector information. The trigger elements are sent to the CTC L1 trigger logic. The CTC forms subtriggers from the information of various subsystems and makes a L1 decision. This decision is sent to the STC system in form of the L1 Keep signal. The STC system sends the L1 Keep signal to the parts of the subsystem where the pipelines are stopped. L2 information is sent from the subsystems to the L2 trigger and if the L2 decision is positive the readout of the detectors begins. Events that are not triggered are overwritten in the pipelines. The STC system can operate in different modes. It does not have to be connected to the CTC system as it is able to generate the clock signal and trigger decisions also autonomously. These modes are needed for standalone tests of a system during debugging or development phases.

The different parts of the STC system have different tasks. The Fast Card simply receives the fast output signals of the CTC and sends them on the STC backplane. The Fanout Card transfers the signals to the rest of the subsystem where the signals are needed and can transfer informations back from the different parts of the subsystem. The Fast Card can run in different autonomous modes where the clock and trigger decisions are generated in the card. It provides scalers to count information like e.g. L1 Keeps and bunch crossings. The Slow card receives interrupt requests and passes them through to the STC CPU via VME interrupt cycles. The Trigger Bit Card receives information from the CTC about which triggers have detected a physics event. The information can be used to calculate informations for the L2 trigger and for cross checks of the subsystem. An overviw of the STC system can be found in [19].

Figure 4.2: Structure of a standard STC system

#### 4.2.1 Trigger signals

Several signals are used for the communication between the STC system and the CTC system. Table 4.1 gives a short overview of the different signals. Signals coming from the CTC and going to the STC are called outward signals. Signals generated in the STC and send to the CTC are called inward signals. Fast signals are synchronous to the HERA clock. Slow signals generate interrupt cycles on the VME bus, or the status of the signal can be read or set in special registers on the STC cards. Slow signals are not synchronous to the HERA clock.

| Direction             | Signal type  | Trigger signal        | Shortcut |

|-----------------------|--------------|-----------------------|----------|

|                       |              | Hera Clock            | HCk      |

|                       | Fast Signals | Pipeline Enable       | PEn      |

|                       |              | L1 Active             | L1Atv    |

|                       |              | L1 Keep               | L1Kp     |

|                       |              | L2 Keep               | L2Kp     |

|                       |              | Fast Clear            | FsClr    |

|                       |              | First Bunch           | FrsBu    |

| $CTC \rightarrow STC$ |              | Filled Bunch          | FillBu   |

|                       |              | Run                   | Run      |

|                       | Slow Signals | All Front End Ready   | AFER     |

|                       |              | L2 Keep               | L2Kp     |

|                       |              | L3 Keep               | L3Kp     |

|                       |              | L3 Reject             | L3Rej    |

|                       |              | Prepare Run           | PreRun   |

|                       |              | Terminate Run         | TermRun  |

|                       |              | Subsystem Timeout     | SubSyto  |

| $STC \to CTC$         | Slow Signals | Front End Ready       | FER      |

|                       |              | L3 Keep Acknowledge   | L3KpAck  |

|                       |              | L3 Reject Acknowledge | L3RejAck |

Table 4.1: Trigger signals

Hera Clock (HCk): This fast signal is the most important signal distributed by the CTC because all fast signals are synchronized to the HERA clock. The frequency of the Hera clock is  $f_{HCk} = 10.40975$  MHz. The time period between two ep interactions is  $\Delta t_{BC} = 96.0638$  ns. This period of time is named one bunch crossing (BC).

Pipeline Enable (PEn): This fast signal shows the subsystem when to start and stop the pipeline for data storage. After a L1 Keep the Pipeline Enable signal drops. It is reactivated after a Fast Clear signal.

- L1 Active (L1Atv): This fast signal shows the subsystem if the L1 trigger is ready to process trigger decisions. After a L1 Keep the L1 Active signal drops. It is reactivated a programmable number of bunch crossings after the Pipeline Enable Signal (current value: 145 BC).

- L1 Keep (L1Kp): This fast signal is sent by the CTC after a positive decision of the central L1 trigger decider. After the L1 Keep signal the pipeline is stopped and the subsystem waits for a L2 trigger decision while it prepares the readout.

- L2 Keep (L2Kp): This signal is sent by the CTC as a fast and a slow signal after a positive decision of the L2 trigger. When a L2 Keep signal is broadcasted the Frontend Ready signal distributed by the subsystem will drop and the readout starts.

- Fast Clear (FsClr): The Fast Clear signal restarts the cycle of data taking. Three conditions can force a Fast Clear signal:

- All Frontend Ready AND All L3 Keep Acknowledge

- All Frontend Ready AND L3 Reject

- L2 Reject

- 1 BC after the Fast Clear Signal the Pipeline Enable signal is broadcasted. The L1 Active signal rises 145 BC after the Fast Clear.

- First Bunch (FrsBu): The maximum number of bunches that can be stored in the accelerator storage rings is 210. The fast signal First Bunch defines the bunch that is counted as the first bunch.

- Filled Bunch (FillBu): Not all of the possible 210 bunches in the storage rings are filled with particles. The fast signal Filled Bunch gives the option to just trigger the events that come from filled bunches.

- Run (Run): This fast signal is active when a run and normal data taking is going on.

- All Front End Ready (AFER): This slow signal is broadcasted by the CTC to inform the subsystem that all other subsystems are ready for a new data take cycle. After the All Frontend Ready signal the Fast Clear signal is broadcasted if all subsystems have acknowledged the L3 Reject or L3 Keep signal. The All Frontend Ready signal is an AND of all Frontend Ready signals of all subsystems.

- L3 Keep (L3Kp): This slow signal is sent by the CTC after a positive decision of the L3 trigger logic. This can be any time between L2 Keep and L3 timeout. It strictly excludes the L3 Reject signal. The signal means that the event is now allowed to be sent to the central DAQ. For the HERA 2000 upgrade a L3 software trigger is planned.

- L3 Reject (L3Rej): This slow signal is sent by the CTC at least 10  $\mu$ s after the L2 Keep signal and earlier than 800  $\mu$ s after the L2 Keep (L3 timeout). L3 Reject and L3 Keep exclude each other strictly. When the L3 Reject signal is received by the subsystem the readout of the data has to be stopped and the data has to be deleted.

- **Prepare Run** (PreRun): The slow signal Prepare Run tells the subsystem to prepare all the different parts of the subsystem for normal data taking and to write the Runstart Record.

- Terminate Run (TermRun): The slow signal Terminate Run ends the run and gives the subsystem the opportunity to clean up their system units and to write the Run End Record.

- Subsystem Timeout (SubSyto): This slow signal is sent if the data taking in the event building is not possible or a subsystem does not respond to the CTC.

- Front End Ready (FER): This signal is sent by the subsystem to the CTC when the hardware is ready to accept a new L1 Keep and the pipeline is prepared for new events by deletion of all old events. At the beginning of a run the Frontend Ready signal is sent when the subsystem is ready for the first L1 Keep.

- L3 Keep Acknowledge (L3KpAck): This signal is sent by the subsystem to the CTC. It shows that the software of the subsystem has taken note of the L3 Keep.

- L3 Reject Acknowledge (L3RejAck): This signal is sent by the subsystem to the CTC to indicate that it has noticed the L3 Reject. If the subsystem handles L3 Rejects it sends the signal after finishing its interrupt routine.

### 4.2.2 Trigger signal timing

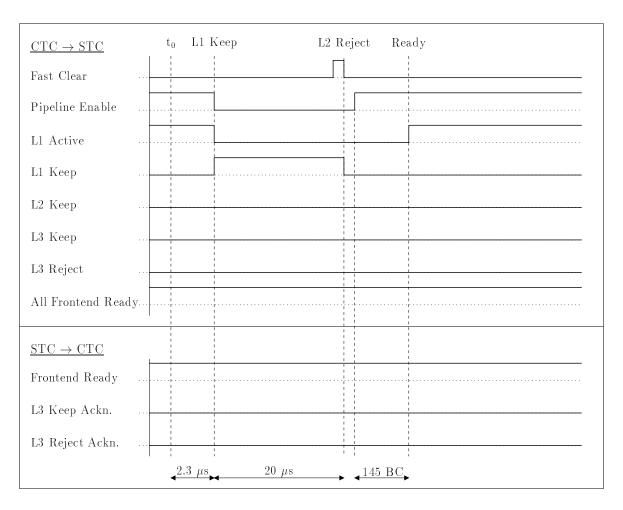

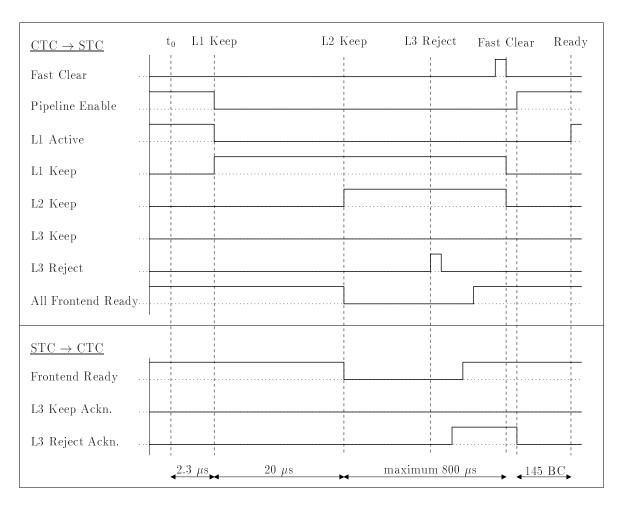

Three different possibilities of timing procedures are possible in a normal run situation without an abort of the run or other special cases. The L2 Reject, the L2 Keep with a L3 Reject and with a L3 Keep are possible. Figure 4.3, 4.4 and 4.5 illustrate the different procedures.

#### Trigger signal timing: L1 Keep, L2 Reject

- 1. L1 Keep signal switches Pipeline Enable and L1 Active to low.

- 2. Pipelines stop. Subsystem prepares Readout. Waiting for L2 Keep.

- 3. L2 Reject (Fast Clear) switches L1 Keep to low. Pipeline Enable rises to high.

- 4. After 145 BC L1 Active rises to high.

- 5. System waits for new event.

Figure 4.3: Trigger signal timing – L1 Keep, L2 Reject

#### Trigger signal timing: L1 Keep, L2 Keep, L3 Reject

- 1. L1 Keep signal switches Pipeline Enable and L1 Active to low.

- 2. Pipelines stop. Subsystem prepares Readout. Waiting for L2 Keep.

- 3. L2 Keep signal starts readout.

- 4. Front End Ready and All Front End Ready go low.

- 5. L3 Reject signal stops readout.

- 6. After recovering from readout abort subsystem sends Front End Ready signal.

- 7. CTC sends All Front End Ready after it receives Front End Ready from subsystems.

- 8. Subsystem sends L3 Reject Acknowledge.

- 9. Fast Clear resets L1 Keep, L2 Keep and Pipeline Enable.

- 10. After 145 BC L1 Active rises to high. System waits for new event.

Figure 4.4: Trigger signal timing – L1 Keep, L2 Keep, L3 Reject

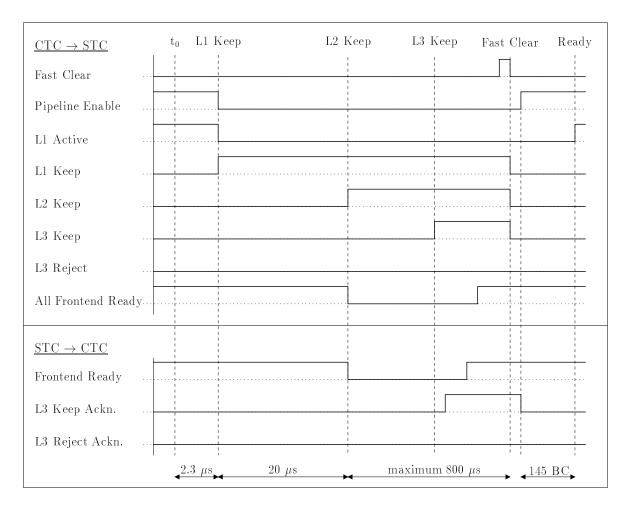

#### Trigger signal timing: L1 Keep, L2 Keep, L3 Keep

- 1. L1 Keep signal switches Pipeline Enable and L1 Active to low.

- 2. Pipelines stop. Subsystem prepares Readout. Waiting for L2 Keep.

- 3. L2 Keep signal starts readout.

- 4. Front End Ready and All Front End Ready go low.

- 5. L3 Keep validates readout. L3 Keep Acknowledge is sent to CTC.

- 6. After readout is finished Front End Ready signal is sent.

- 7. CTC sends All Front End Ready after it receives Front End Ready from subsystems.

- 8. Fast Clear resets L1 Keep, L2 Keep and Pipeline Enable.

- 9. After 145 BC L1 Active rises to high.

- 10. System waits for new event.

Figure 4.5: Trigger signal timing – L1 Keep, L2 Keep, L3 Keep

#### 4.2.3 STC cards

All STC cards are supposed to be housed in a special VME crate. The backplane connection P1/J1 conforms fully to VME standard, while P2/J2 does not. The P2/J2 connection consists of a four row 128 contact connector. It is actually five rows wide with the central row empty. The cards require the non VME ECL supply voltage of -5.2 V. The voltage is fed in through the bottommost contacts of P2/J2. Information on the different cards can be found in [20] (Fast Card), [21] (Slow Card) and [22] (Fanout Card).

#### Fast Card

The Fast Card is described in [20]. It is connected via a multiconductor twisted pair cable to the CTC. During normal DAQ it simply receives the fast outward signals and passes them on the P2/J2 backplane of the STC crate, where they may be connected via wire wrap to the Fanout Cards. In addition there are some functions in the Fast Card which are not simply passive and serve useful purposes, the FER function, scalers and local L1

and L2 trigger logics to generate local L1 and L2 decisions without a connection to the CTC.

**Modes** There are five basic modes of operation, numbered from 0 to 4. They mean different levels of independence from the CTC.

- 0: Submissive. Normal mode during correlated data taking in the entire detector.

- 1: Data Autonomous L1/L2 Submissive. The Fast Card receives the clock, L1 and L2 info and the machine related signals from the CTC. The subsystem data will be stored locally and will not go to the event building.

- 2: Data and L2 Autonomous L1 Submissive. Similar to mode 1 but the STC may do its own L2 decision and timing.

- 3: Trigger Autonomous Clock Submissive. The STC receives just the HERA clock from the CTC. Trigger actions in the STC are completely independent from the CTC.

- 4: Clock Autonomous. Same as mode 4 but a local quartz oscillator generates the HERA clock in the STC system.

- **HERA clock circuits** The central HERA clock is available via a differential pair of the outward cable or via a BNC connector. In addition a quartz oscillator on the card can generate the HERA clock. A clock monitor circuit checks the clock for errors.

- Local L1 logic Every local trigger in the trigger logic has an allocated flip flop which is set in synchronism with the HERA clock if the trigger and gating conditions are fulfilled. The gating conditions can be the L1 Active signal, the Filled Bunch signal or an external input. The flip flops may be read via VME and have an output on the P2 backplane. In mode 3 and 4 three local L1 triggers can be operated. Two different detector triggers intended to accept trigger signals from the subsystems own detector, and an auto-synchronizing test trigger. The local detector trigger can be scaled down not triggering every event. The flip flop of the unscaled trigger has a rear output on the P2 backplane. The gating condition for the triggers are the L1Atv signal, the Run signal and the FillBu signal if needed. The auto-synchronizing test trigger is intended to be set by pulse generators through front or rear inputs or by a bus trigger.

- Local L2 control In mode 2 to 4 the subsytem can make its own L2 decisions, either upon the L1 Keep events offered by the STC in mode 2 or upon its own L1 Keeps. The Fast Card does not contain any L2 deciders. A clocked hardwired L2 decider has to be located somewhere not too far away. The Fast Card senses the output level of the decider a presettable number of HCk cycles after L1 Keep. Depending on the status of this level the Fast Card takes either the L2 Reject turn or continues into L2 Keep. If there is no local decider a L2 decision may be forced into both ways by writeable control bits.

- FER logic There are two possible sources for the FER signal. Either a flip flop on the Fast Card or an external signal, e.g. the logical AND of many status signals of readout

electronics. The selection between these modes is done by a control bit FER mode, which may be set through VME. An automatic setting of the FER level independent from any data readout can be done for test purposes. A 16 bit number written to a register gives the set delay after the L2 Keep in HERA clock cycles. A one HCk long FER pulse is available on P2 after FER has gone from false to true. This pulse can be used to reset the local L1 flip flops in mode 1 to 4.

**Restart logic** When the handling of an event is finished by the L2 Reject signal or by the FER signal becoming true again, the fast signals must be switched to their normal state in a defined way. In mode 0 this is done by the CTC. For the other modes there is a restart logic on the Fast Card.

Scalers The Fast Card contains several scalers that can be read slowly via the VME bus at a certain time while the scalers continue counting. The following scalers are available: a 8 bit bunch scaler, a 32 bit revolution scaler gated by the FrsBu signal, a 40 bit all crossing scaler and a 40 bit crossing during L1Atv scaler.

#### Slow Card

The Slow Card is described in [21]. The main job of the Slow Card is to receive interrupt requests and passing them through VME interrupt cycles to the subsystem processor. The Slow Card is connected to the CTC via a multiconductor flat cable connected to the P2/J2 backplane. This connection follows the RS423 standard. 8 full and 1 reduced interrupt channel are connected through a wire-wrap matrix and three priority encoders to VME interrupters. The interrupt requests can come from the CTC or from a VME write cycle. Two 32 bit gated scalers with common reset for counting L1 Keeps and L2 Keeps are available. A four channel outward information bit connection to the CTC gives information about the status of the CTC.

Information bit logic Four information bits are received from the CTC which can be made available by a local wire wrapping on the P2 connector. Their status can be read from the VME bus and is indicated by front panel LEDs.

Scaler logic There are two 32 bit synchronous and gated scalers on the card for counting the L1 Keep and the L2 Keep. Their clock, gate and common reset inputs are accessible through the P2 connector. The contents of the scalers can be read via VME.

Interrupt request logic Interrupt requests coming from the CTC or a VME write cycle set the appropriate interrupt flip flop. There are eight identical interrupt channels. Eight signals coming from interrupt flip flops and one received from the Fast Card L2 Keep flip flop are logically ANDed with their mask register and can be connected by the user via wire wrapping to one of three priority encoders. Each of these encoders has eight inputs. The OR output of every encoder is connected to the driver of one IRQ line on the VME bus. During the VME acknowledge cycle an interrupt vector (status byte) is placed on the data lines.

#### Fanout Card

The Fanout Card is described in [22]. The Fanout Card accepts six different outward signals from the STC's Fast Card or from other signal sources. It passes them on to the subsystem electronics. The signals can be manipulated, e.g. delayed, disabled, simulated, etc. in the Fanout Card. From the internal logics the signals are fanned out fivefold to identical cable ports and to front NIM outputs. Each cable port contains two differential inputs for inward signals. The inward signals are available at the backplane connector P2/J2 in high level form. A lot of features of the card can be controlled and read via the VME bus.

Outward fast signal logic The outward fast signals (mainly HCk and PEn) can be manipulated. VME programmable delays can delay the HCk and the PEn signal. A PEn Afterrun logic makes it possible to delay the true to false transition of the PEn signal for a number of clock phases. This logic can be programmed via the VME bus. A Gated Clock logic can mix the HCk and the PEn signal to produce a clock wave that lasts as long as PEn is active. The Artificial Signal logic can simulate the PEn signal independent from the inputs. The duration of the signal can be programmed via the VME bus and the puls can be triggerd via NIM input or the VME bus. The signals will be synchronised to the HCk signal. The outputs of this logic can be mapped via jumpers in different ways on the cable ports and NIM outputs.

Outward slow signal logic The outward slow signals can be delayed the same way as the fast signals. An Artificial Signal logic can simulate the slow signals in a same way like the PEn signal. The outputs of the logic can be mapped on different outputs on the cable ports and the NIM outputs.

Inward signal logic The inward signals coming from the subsystem trigger electronics are available on the backplane connector P2/J2 or can be read via the VME bus. A connection test logic can test if a connection is broken. The test logic can be controlled via the VME bus. A logical AND programmed via the VME bus can be formed on the inward signals. The AND can be extended over several cards.

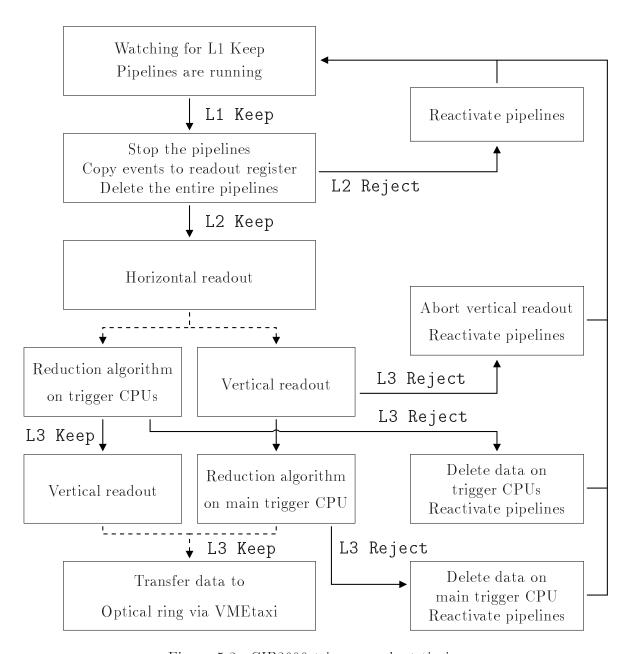

## 4.3 CIP2000 trigger STC and readout control system

The main control unit of the trigger and readout part of the CIP2000 trigger system is the main trigger CPU. It manages the interrupt handling and the writing and reading of registers in the STC cards via a VIC link to the STC crate. The communication between the different trigger CPUs is implemented via the pVIC link. The software running on the CPUs uses a state machine structure switching from state to state depending on control registers set by the main trigger CPU. The different states of the CPUs are called modes. Every trigger CPU has a mode register showing other CPUs the present mode it is working in. A remote register that can be set from the main CPU shows the trigger CPU what action to take and what mode to switch to. The trigger cards are controlled